# Design of 125-Level Asymmetrical Multilevel Inverter with Reduced Switch Count

# N V Vinay Kumar, T Gowri Manohar

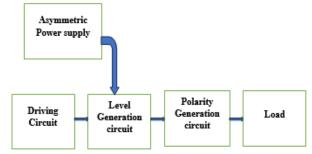

This paper provides a unique reduced Abstract: component-count-efficient topology for 125-level asymmetrical multilevel inverter. The proposed design uses asymmetric DC sources and an H-bridge to produce an output voltage that can reach a maximum of 125 levels. The design and development of a multi-level inverter with a stacked half-bridge architecture that generates a 125-level output with excellent power quality is the object of the current research. The MOSFETs are triggered using a fundamental frequency switching technique that has been modified for output voltage level control. At its output, the level production circuit exclusively generates positive levels. Look-up tables are employed to regulate MOSFETs, and an H-bridge circuit is used to create polarities. 125 levels of output result in a nearly sinusoidal voltage waveform, which will give a nearly sinusoidal voltage waveform without the use of filters. The proposed work is Simulated in MATLAB/Simulink software.

OPEN ACCESS

Keywords: Multilevel Inverter, Pulse width Modulation Technique, Total Harmonic Distortion.

# I. INTRODUCTION

${f M}$ ultilevel inverters have recently attracted attention due to their substantial power operation capacity and a number of advantages, including reduced harmonics, decreased electromagnetic interference, high power quality, and fewer switching losses [1]. Employing a power electronic circuitry made up of multiple power semiconductor switches, these MLIs produce a stepped voltage waveform at their output using a variety of DC sources [2]. The level can be expanded to further enhance waveform quality. However, because there are extra devices in the circuit, which results in a higher cost, ensuring the reliability, as well as the performance of MLI, is a difficult task [3]. There are three main types of MLIs: flying capacitors (FC), cascaded H-bridges (CHB), and diodes clamped or neutral point clamped (NPC) [4]. Single DC source and Multi DC source are the names of the CHBMLI. The CHBMLI are parallelly coupled in a single DC source. The CHB multilevel inverters for multi-DC sources use an arrangement of H-Bridge cells with separate DC voltage sources connected to each cell.

Manuscript received on 03 June 2024 | Revised Manuscript received on 05 July 2024 | Manuscript Accepted on 15 July 2024 | Manuscript published on 30 July 2024.

\*Correspondence Author(s)

**N V Vinay Kumar\***, Department of Electrical & Electronics Engineering, Sri Venkateswara University College of Engineering, Sri Venkateswara University, Tirupati, India. Email: <u>vinaynanda.svu@gmail.com</u>, ORCID ID:0000-0002-6266-9928

T Gowri Manohar, Department of Electrical & Electronics Engineering, Sri Venkateswara University College of Engineering, Sri Venkateswara University, Tirupati, India. Email: <u>gowrimanohart@gmail.com</u>, ORCID ID: 0000-0003-0441-6022

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an <u>open access</u> article under the CC-BY-NC-ND license <u>http://creativecommons.org/licenses/by-nc-nd/4.0/</u>

Retrieval Number: 100.1/ijsce.H991413080724 DOI: <u>10.35940/ijsce.H9914.14030724</u> Journal Website: <u>www.ijsce.org</u>

Bipolar and unipolar multilevel converters, which can generate levels naturally or using an H-bridge, are the two main types available. MLIs can provide output voltage values that are both positive and negative. Some additional multilevel converters produce just positive polarity in the first stage, and in the second stage, an H-bridge changes the polarity waveform to bipolar, producing AC voltage as a positive and negative half-cycle. On the other hand, the H-bridge refers to the "polarity-generation part" while the first component, refers to the "level-generation part." H-bridge topologies may have fewer components, but it's possible that H-bridge circuits can withstand a lot of switch stress. The level-generation portion of the suggested architecture in [5] [12] [13] can be built by connecting sub modules in series. H-bridge is inserted as the polarity-generation component at the conclusion of the series connection. Each switch in the level-generation section should withstand the voltage of the relevant DC source(s).

Based on the magnitudes of the DC voltage, the CHB inverter is divided into symmetric and asymmetric types using a variety of single-phase H-bridge topologies. All DC voltage sources in a symmetric MLI are of identical magnitude, in contrast to an asymmetrical MLI where the magnitudes are not. For the same amounts of output voltage, asymmetrical topologies required fewer switching devices and voltage sources than symmetrical topologies. In contrast to typical topologies, the topology described in this paper for a 125-Level Asymmetrical Multilevel Inverter required fewer switching devices

#### II. MULTILEVEL DC LINK INVERTER TOPOLOGY

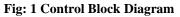

The multilayer DC link inverter (MLDCL) is one of the most popular reduced switches MLI topologies, as suggested in (NV, V. K, 2023) [6]. It is an independent type MLI, and separate DC sources are needed depending on the quantity of output levels (R. Agrawal and S. Jain, 2017) [7] [14] [15] [16]. For the same amounts of output voltage, asymmetrical topologies required fewer switching devices and voltage sources than symmetrical topologies. The MLI configuration, shown in Fig.2, consists of an H-bridge inverter circuit called the Polarity generation circuit and an asymmetric basic circuit called the Level generator unit. Compared to a level generation unit, the switches in the polarity generation circuit will be under more stress. MLDCL is a hybrid version of MLI that consists of a stage for level generation and a stage for polarity generation. The circuit block diagram for the 125-level inverter output is shown in Fig.2, where the Level Generation Circuit and Polarity Generation Circuit are both controlled by the Driving Circuit's control signals.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

1

When compared to their symmetric equivalents, asymmetric structures are capable of producing higher levels of output for comparable numbers of semiconductor devices and voltage sources.

The MLDCL inverter topology, which consists of six DC sources, is shown in Figure 2. The level generating stage creates positive and zero voltage levels in the form of a stair-step waveform. In contrast, the H-Bridge-based polarity generating stage alternately inverts each second half-cycle of the waveform formed by the level creation stage into negative levels, providing an output that resembles a sine wave (Venkataramanaiah, Y. Suresh, and A. K. Panda, 2017) [8]. Based on an asymmetrical DC source arrangement, 125 levels of output voltage are produced using the same topology as in Fig. 2. By applying the binary technique, the DC sources are identified for 125 output levels using geometric progression as follows. (N. V. Vinay Kumar and Tenepalli Gowri Manohar, 2024) [9].

In contrast to the symmetrical structure, it is possible to generalize the number of levels and switch needed in an asymmetrical MLDCL inverter as follows (M. D. Siddique et al.,2019) [10].

$$N_{L,asym} = 2n + 1$$

,  $N_{S,asym} = 2n + 4$

This topology is based on a full bridge cascaded H-bridge inverter and one-stage sub-multilevel converter units connected in series. The power semiconductor switches of the ASCHBMLI are managed by a low-frequency pulse width modulation method. Instead of the many benefits of MLIs, reliability problems are a major concern because more components are needed to reduce THD. To boost reliability while reducing THD, researchers face a crucial problem.

This paper's major goal is to employ fewer switches while adding more levels to the output voltage. In comparison to standard topologies, the suggested topology provides high power capability with lower total harmonic distortion (THD), commutation losses, and the number of switching devices and voltage sources.

This paper presents a new topology based on asymmetrical multilevel inverter (ASMLI), shown in Fig. 2. It required six unequal voltage sources (V1, V2, V3, V4, V5 and V6) and twelve unidirectional switches (S1, S2, S3, S4....S12), which is a combination of IGBT with antiparallel diode to produce the 125-Level single phase output voltage that is found in nature. Due to the unidirectional nature of every semiconductor switching component employed in this circuit, the number of MOSFETs and driver circuits stays constant. The variables that affect switching losses in a multilayer inverter circuit are current, blocking voltage, and switching frequency. The condition of each switch in the level generation unit is shown in Table 1. S1, S2, S3, S4....S12 of the level generating unit, along with T1, and T2 of the polarity generation unit, can be used to create a total of 125 levels. S1, S2, S3, S4.....S12 can all be turned off to achieve zero level. Since the negative half cycle will be in symmetry with the positive cycle, it can be produced by combining T3 and T4 of the polarity production unit with S1, S2, S3, S4....S12 of the level generation unit.

Fig: 2 Proposed 125 level MLDCL Inverter

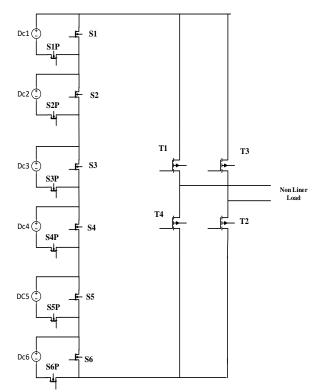

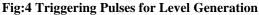

## III. APPROCH FOR PULSE WIDTH MODULATION

In a multilayer inverter (MLI), modulation techniques are employed to create a train of switching pulses that create sinusoidal waveforms at the output voltage. Reference signal and carrier signal are contrasted in modulation techniques [11]. It is necessary to use carrier waves for N-Level inverters (N-1). The MLDCL inverter design does not necessitate the use of a specific modulation approach, with the exception that there may be some variation in the combos of carrier signals that must be compared with the reference signal when generating switching pulses using relational operators. The carrier-based PWM approach is the most popular sort of PWM that may be employed. Every time the

Retrieval Number: 100.1/ijsce.H991413080724 DOI: <u>10.35940/ijsce.H9914.14030724</u> Journal Website: <u>www.ijsce.org</u> Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

#### International Journal of Soft Computing and Engineering (IJSCE) ISSN: 2231-2307 (Online), Volume-14 Issue-3, July 2024

carrier signal is compared to the reference signal, which must always be stronger, the switching pulse displays "1," otherwise it displays "0." The switching pulse is created by adding the comparison results between the reference signal and carrier signal, and the voltage levels are then produced.

Fig:5 Triggering Pulses for Polarity Generation

#### **IV. SIMULATION RESULTS**

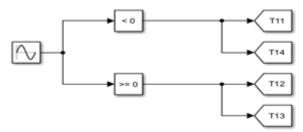

Below is an analysis of the 125-level inverter's results with the ideal number of switches. the following list of input

Fig:6 Simulation Result for 125 Level Output

Retrieval Number: 100.1/ijsce.H991413080724 DOI: <u>10.35940/ijsce.H9914.14030724</u> Journal Website: <u>www.ijsce.org</u> voltage sources is used: V1=3.8v, V2=7.6v, V3=15.2v, V4=30.4v, V5=60.8v, V6=121.6v. The output voltage is supposed to have a 50Hz frequency.

TABLE III. Comparison of Required Components between Proposed and Conventional Topologies for 125-level MLI

| MLI<br>Components      | Diode<br>Clamped | Flying<br>Capacitor | Cascaded<br>H-Bridge | Proposed<br>Topology |

|------------------------|------------------|---------------------|----------------------|----------------------|

| Switching<br>Devices   | 248              | 248                 | 248                  | 16                   |

| Clamping<br>Diodes     | 15252            | -                   | -                    | -                    |

| DC Split<br>Capacitor  | 123              | 123                 | -                    | -                    |

| Clamping<br>Capacitors | 0                | 7626                | -                    | -                    |

| DC Sources             | 1                | 1                   | 62                   | -                    |

| Total                  | 15624            | 7998                | 310                  | 16                   |

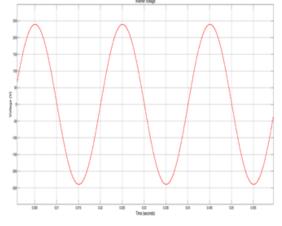

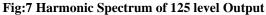

The semiconductor switching MOSFET is provided the output of the pulse generator. These pulses are 1V in magnitude. The harmonic of inverter output voltage is 0.01% which is within the tolerance limit specified by the IEEE standard for harmonics (IEEE 519). Fig. 7 depict this. The 125-level output for the proposed inverter is shown in Figure 6. Simulation is performed for the proposed circuit with MATLAB/SIMULINK.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

3

#### V. CONCLUSION

The paper deals with A 125-Level Asymmetrical Cascaded Multilevel inverter. The Pulse width modulation technique is used for controlling the MOSFET switches. This paper proposes a medium voltage system-optimized multilayered inverter architecture. The main benefit of this design is its simplicity, which allows for a reduction in both the complexity of the driving circuit and the size of the multilayer inverter. The MATLAB/SIMULINK platform is used for simulation. The output is 125 levels with a THD of 0.01%. Additionally, the outcomes can be used to deduce the characteristics of this topology for increasing output levels. The recommended asymmetric topology has been compared to other topologies in terms of the key characteristics. As can be observed, the MLDCL asymmetric structure inverter has lower blocking voltage values for semiconductor switching devices than other topologies that employ asymmetric structures. Simulated outcome for the suggested methods is presented. It has been demonstrated that an inverter with the proposed topology requires fewer MOSFETs. We may reduce the number of gate drivers by employing this topology, which will also result in a smaller circuit.

## ACKNOWLEDGMENT

I/We hereby declare that this submission is entirely my work, in my own words, and that all sources used in researching it are fully acknowledged and all quotations properly identified.

| Funding                                        | No, I did not receive.                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Conflicts of Interest                          | No conflicts of interest to the best of our knowledge.                                                                                                                                                                                                                                                                                                                                         |  |  |

| Ethical Approval and Consent<br>to Participate | No, the article does not require ethical approval and consent to participate with evidence.                                                                                                                                                                                                                                                                                                    |  |  |

| Availability of Data and<br>Material           | Not relevant.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Authors Contributions                          | Conceptualization was done by N V<br>Vinay Kumar (NVVK) and T Gowri<br>Manohar (TGM); validation was done<br>by NVVK and TGM; formal analysis<br>was done by NVVK; investigation<br>was done by NVVK; resources were<br>done by NVVK; writing—original<br>draft preparation were done by<br>NVVK; writing—review and editing<br>were done by TGM; supervision was<br>done by TGM. NVVK and TGM |  |  |

#### **DECLARATION STATEMENT**

participated in its design and coordination and helped to draft the manuscript. Both authors have read and agreed to the published version of the manuscript and approved the final manuscript

## REFERENCES

- Trabelsi, M., Vahedi, H., & Abu-Rub, H. (2021). Review on single-DC-source multilevel inverters: Topologies, challenges, industrial applications, and recommendations. IEEE Open Journal of the Industrial Electronics Society, 2, 112-127. https://doi.org/10.1109/OJIES.2021.3054666

- Vemuganti, H. P., Sreenivasarao, D., Ganjikunta, S. K., Suryawanshi, H. M., & Abu-Rub, H. (2021). A survey on reduced switch count multilevel inverters. IEEE Open Journal of the Industrial Electronics Society, 2, 80-111. <u>http://dx.doi.org/10.1109/OJIES.2021.3050214</u>

- Chethan, M., & Kuppan, R. (2024). A review of FACTS device implementation in power systems using optimization techniques. *Journal of Engineering and Applied Science*, 71(1), 18.<u>https://doi.org/10.1186/s44147-023-00312-7</u>

- Vijeh, M., Rezanejad, M., Samadaei, E., & Bertilsson, K. (2019). A general review of multilevel inverters based on main submodules: Structural point of view. IEEE Transactions on Power Electronics, 34(10), 9479-9502. http://dx.doi.org/10.1109/TPEL.2018.2890649

- K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu, and S. Jain (2016), "Multilevel Inverter Topologies with Reduced Device Count: a Review", IEEE Transactions on Power Electronics, vol. 31, no. 1, pp. 135–151. <u>https://doi.org/10.1109/TPEL.2015.2405012</u>

- NV, V. K. (2023). A comprehensive survey on reduced switch count multilevel inverter topologies and modulation techniques. Journal of Electrical Systems and Information Technology, 10(1), 3. https://doi.org/10.1186/s43067-023-00071-8

- R. Agrawal and S. Jain (2017), "Comparison of Reduced Part Count Multilevel Inverters (RPC-MLIs) for Grid Interfacing", IETE Journal of Research, pp. 1–14. https://doi.org/10.1080/03772063.2017.1367262

- Venkataramanaiah, Y. Suresh, and A. K. Panda (2017), "A Review on Symmetric, Asymmetric", Renewable Sustainable Energy Reviews, vol. 76, pp. 788–812. <u>https://doi.org/10.1016/j.rser.2017.03.066</u>

- N. V. Vinay Kumar and Tenepalli Gowri Manohar (2024), "Meta Heuristic Algorithm Based Novel Dstatcom Architecture for Power Quality Improvement". International Journal of Experimental Research and Review, 38, 119-131. https://doi.org/10.52756/ijerr.2024.v38.011

- Marif Daula Siddique, Saad Mekhilef, Noraisyah Mohamed Shah, Adil Sarwar, Mohammad Tayyab(2019), "Low Switching Frequency Based Asymmetrical Multilevel Inverter Topology With Reduced Switch Count", IEEE Access, vol 7, pp 86374-86383 https://doi.org/10.1109/ACCESS.2019.2925277

- Juárez-Abad, J.A., Barahona-Avalos, J.L., Linares-Flores, J.: PWM techniques for an asymmetric multilevel binary inverter: an FPGA-based implementation. IET Power Electron.14, 1529–1539 (2021). https://doi.org/10.1049/pel2.12131

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

Retrieval Number: 100.1/ijsce.H991413080724 DOI: <u>10.35940/ijsce.H9914.14030724</u> Journal Website: <u>www.ijsce.org</u>

- M.E, M. R., & Sudha, K. R. (2019). Asymmetrical Cascade Multilevel Inverter Design using Modified Level Shift Pulse Width Modulation. In International Journal of Recent Technology and Engineering (IJRTE) (Vol. 8, Issue 2, pp. 2650–2659). https://doi.org/10.35940/ijrte.b1843.078219

- R, A., D, V., S, M., M, R., & A, K. (2019). Performance Examination of SEPIC Based Hybrid Cascaded Single-Phase Multilevel Inverter. In International Journal of Engineering and Advanced Technology (Vol. 9, Issue 2, pp. 3644–3648). https://doi.org/10.35940/ijeat.b2288.129219

- Wani, G. H., & Shedge, Dr. D. K. (2019). Design and Development of Microcontroller Based Multilevel Inverter. In International Journal of Innovative Technology and Exploring Engineering (Vol. 8, Issue 10, pp. 1775–1778). <u>https://doi.org/10.35940/ijitee.i8599.0881019</u>

- Karpe, Dr. S. R., Deokar, S., & Shinde, Dr. U. B. (2024). Predictive Controller Strategies for Electrical Drives System using Inverter System. In International Journal of Emerging Science and Engineering (Vol. 12, Issue 7, pp. 27–39). https://doi.org/10.35940/ijese.e4114.12070624

- O. S., A., B. M, Y., & O, O. (2023). Scientific Assessment of Locally and Factory Built 2 KVA Modified Sine Wave Solar Powered Inverters. In Indian Journal of Microprocessors and Microcontroller (Vol. 3, Issue 1, pp. 1–12). https://doi.org/10.54105/ijmm.d4057.033123

## **AUTHORS PROFILE**

N V Vinay Kumar (Corresponding Author) was born in Anantapur city, Andhra Pradesh, India. He received his B.Tech. & M. Tech degree from JNTUA in 2009 & 2012. Currently he is a research scholar in department of Electrical and Electronics Engineering in Sri Venkateswara University college of Engineering, Sri Venkateswara University, Tirupathi,

His research interests include Power Converters, Power quality and Optimization Techniques.

**Prof. T GowriManohar** (Co-Author) was born in Tirupathi City, Andhra Pradesh, India. He is a professor in Dept. of Electrical & Electronics Engg, S.V. University College of Engineering, Sri Venkateswara University, Tirupathi, Andhra Pradesh, India. His research interests include Power System Operation and Control, Power quality and

Power Converters.

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of the Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP)/ journal and/or the editor(s). The Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

Retrieval Number: 100.1/ijsce.H991413080724 DOI: <u>10.35940/ijsce.H9914.14030724</u> Journal Website: <u>www.ijsce.org</u> Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.